Flotherm高級培訓:芯片的熱模型建立

Flomerics中國代表處 90min

芯片的主要結構

并非所有的芯片都包含所有的上述結構;

Die是一定存在的;

多核芯片(多個Die)越來越多了。

陶瓷芯片與塑料芯片

結構區別:芯片的基片(Substrate)材料:陶瓷?塑料?

塑料芯片

- 通常結構更復雜,建模較難

- 價格便宜

- 可靠性差

- 非全氣密封封裝

- 熱性能差,需加強考慮

- 目前為主流的芯片類型

主要應用: ASIC芯片, 邏輯芯片, 內存芯片,低功耗處理器

陶瓷芯片

- 價格昂貴

- 可靠性高

- 良好的電氣性能(fine line widths,

multiple layers)

- 全氣密封裝

- 良好的熱性能

- 應用場合少

主要應用: 高功耗處理器,軍用航空航天用芯片

芯片的熱阻模型

JEDEC定義了半導體芯片的熱屬性定義方法:各種熱阻定義標準;

這些標準可從網站www.jedec.org上免費下載;

JEDEC組織有關熱方面的系列文件位于JESD51 series(JESD51-X)

θjx =(Tj - Tx) /P

熱阻定義:

Tj = Die發熱部位的溫度值die (“junction”)

Tx = 某參考點的溫度值

P = 芯片的功耗

θja 結-空氣熱阻

θja

–最早也是最常用的標準之一

–定義標準由文件JESD51-2給出

θja =(Tj - Ta) /P

–Ta = 環境空氣溫度, 取點為JEDEC組織定義的特定空箱中特定點(Still-Air Test)

–芯片下印制板可為高傳導能力的四層板(2S2P)或低傳導能力的一層板之任一種(1S0P)

θjma 結-移動空氣熱阻

–空氣流速范圍為0-1000 LFM

–定義標準由文件JESD51-6給出

θjma =(Tj - Ta) /P

–Ta = 空氣溫度,取點為風洞上流溫度

–印制板朝向為重大影響因素

θjc 結殼熱阻

–從結點到封裝外表面(殼)的熱阻,外表面殼取點盡量靠近Die安裝區域

θjc =(Tj - Tc) /P

θjb 結板熱阻

–從結點至印制板的熱阻

–定義標準由文件JESD51-8給出

θjb 結板熱阻

θjb =(Tj - Tb) /P

嚴格地講,Theta-JB不僅僅反映了芯片的內熱阻,同時也反映了部份環境熱阻,如印制板。

正因如些, Theta-JB相對于其它熱阻而言,雖然JEDEC組織在99年就發布了它的熱阻定義方式,但是芯片供應商采用較慢。

部份傳熱路徑嚴重不對稱芯片,如TO-263目前尚無該熱阻的定義標準

θjx 使用的局限性

θjx 試圖采用簡單的熱阻表示復雜的芯片傳熱現象

芯片內部的熱傳現象非常復雜,無法使用熱阻來完美表示;

熱阻θjx 無法用于準確預測芯片的溫度,只能提供定性的熱性能對比;

如需準確預測特定工況下芯片的溫度,我們需要其它的方法

熱阻網絡模型-DELPHI模型

DEvelopment of Libraries of PHysical models for an Integrated design environmentDELPHI 項目:從1993年到1996年,由歐盟資助,Flomerics公司負責協調,Alcatel Bell 、Alcatel Espace 、Philips CFT 、Thomson CSF 、Flomerics 、NMRC 等公司合作,旨在開發芯片的簡化熱模型的精確表示方法。

PROFIT項目:同樣由歐盟資助,由Philips公司負責協調,Flomerics、Nokia、Infineon、Philips、ST、Micred、TIMA、等公司合作,旨在開發芯片熱模型的快速建立方法。

項目產生了一系列成果,如芯片的熱阻網絡模型DELPHI標準、JEDEC組織認證的唯一熱模型庫FLOPACK、芯片熱應力分析工具Flo/stress等。

PROFIT 項目

PRediction OF temperature gradients Influencing The quality of electronic products

DELPHI項目

DEvelopment of Libraries of PHysical models for an Integrated design environment

DELPHI模型生成原理

PBGA封裝模型的建立

PBGA封裝特點?

–有機基片Organic substrate

–使用焊球(Solder balls)作為二級互聯

主要應用: ASIC’s, 內存, 圖形顯示,芯片組,通訊等.

PBGA封裝優缺點?

–I/O密度高;

–基片材BT具有較好的電性能;

–加工工藝類似PCB板,成本低廉

–非氣密封裝,不適合于長時工作的芯片或軍用芯片

–Die與基片(Substrate)間的CTE不匹配

–如功耗大于2W,則可能需要加強散熱手段

主要類型的PBGA封裝

由die-up PBGA變化而來

–別名: FSBGA, ChipArrayTM

–焊球間隙較小

–可歸類為Near-CSP

–建模也較困難

–焊球間隙典型值為1mm,0.8mm,0.65mm,0.5mm,0.4mm

–經常缺少明顯可見,比Die尺寸大的Die Pad,因為Die大小與封裝大小相近

–基片(substrate)中每個信號過孔都必須單獨建出;

–在FLOPACK中,別名ChipArrayTM

CBGA封裝模型的建立

主要應用:高功耗處理器,軍事用芯片

主要分為:

1)Flip-Chip

2)BondWire

PQFP封裝模型的建立

Plastic Quad Flat Pack

(thin version called

TQFP)

常用于邏輯芯片, ASIC芯片, 顯示芯片等

封裝外管腳(Lead), 表面貼裝

PQFP封裝模型的建立

PQFP封裝優缺點?

–成熟的封裝類型,可采用傳統的加工方法;

–成本低廉;

–適用于中低功耗且中等數目I/O(50-300),

–熱阻高,不采用Heatslug等附加散熱手段的條件下功耗很難突破2W

–管腳間距難以做得過小(難于小于0.4mm),相對于BGA封裝I/O 數目少.

無散熱器時的主要散熱路徑

–The die and the die flag

–The leadframe

–The board

注意:在Lead數目較多的情況下,Bondwires的傳熱份額可能高達15%,但是在熱測試芯片中,由于Bondwires數目較少,忽略了這部分熱量注意:一部分熱量由芯片傳至散熱器上,又有可能重新傳遞回芯片上.

SOP/TSOP封裝模型的建立

Small Outline Package

Low profile version known as Thin Small

Outline Package (TSOP)

類似于PQFP, 只是只有兩邊有管腳

廣泛應用于內存芯片

常見的類型

- 常規

- Lead-on-Chip

部分芯片建模時可將各邊管腳統一建立;

管腳數較小應將各管腳單獨建出.

fused lead 一定要單獨建出

Tie bars 一般可以忽略.

QFN封裝模型的建立

主要用于替換引腳數小于80的引線裝芯片(主要是TSOP and TSSOP)

尺寸較小,同時相對于TSOP/TSSOP散熱性能好

Theta-JA 通常只有TSSOP芯片的一半左右

主要傳熱路徑:Die --> Die Attach Pad--> Exposed Pad --> PCB

次要傳熱路徑:Lead(最好各個管腳單獨建出)

PCB板下(Exposed Pad下方)通常添加熱過孔以加強散熱

CSP封裝模型的建立

封裝相對于Die尺寸不大于20%

–主要應用于內存芯片,應用越來越廣泛

–尺寸小,同時由于信號傳輸距離短,電氣性能好

–種類超過40 種

如封裝尺寸相對于Die,大于20%但接近20%,則稱為Near-CSP

Micro-BGATM封裝模型的建立

為早期的一種CSP 設計

常用于閃存芯片

Traces 排布于聚酰亞胺的tape 層

Die與Tape之間有專用的Elastomer

采用引腳Lead將電信號由die傳遞至traces

焊球可較隨意排布

Die 可放在中心,也可以偏置

主要傳熱路徑: Die --> elastomer --> solder balls --> board

Lead傳導熱量較少,很多情況下可忽略

Elastomer導熱能力差,為主要的散熱瓶頸

焊球要求單獨建出

Tape中Trace的傳導較少,但是不能忽略

Solder Ball也夠成相對較小的熱阻(相對于Elastomer)

其它的CSP芯片

Fine-Pitch BGA (ChipArrayTM, FSBGA)

–類擬于PBGA, 更焊球間距更小

–Fan-in traces

–所有的過孔都必須單獨建出

MicroStarTM / FlexBGATM

–類擬于ChipArray, 但基片材料為tape 而非BT

堆棧封裝(Stacked Packages)模型的建立

開始應用于內存領域(stacked TSOP)

近來應用到了面陣列封裝領域

堆棧裸片封裝(Stacked-Die Packages)的建模

別名SiP (System in Package)

通常堆棧2-4層裸片

–目前也在研發6層或更多數目的堆棧裸片

當所有的功能難以集中在單片裸片中時應用

常見的應用: Flash/SRAM, ASIC/Memory, Memory/Logic,

Analog/Logic

In area array or leaded package outlines

加工困難,第層裸片都必須加工為特別薄(50微米級)

需要精細的電路設計和散熱設計

尚無成熟的熱簡化模型

芯片常用于體積要求較小的手機或其它移動電子設計

芯片的結構建模Die

晶片(Dice),表面附有集成電路

通常為硅制,部份為砷化鎵制(微波芯片或高速芯片)

集成電路位于表面一側的細節內,也可稱active surface

通常可將Die表面視為均溫(熱測試芯片);

部分芯片Die表面溫差可在10℃以上,FLOPACK可處理

注意多核芯片現在越來越多了

芯片的結構建模Die Pad

Die Flag Die

在塑料封裝中Die通常位于一金屬薄片上(Die Pad 或Die Flag)

Die Pad通常為銅制,通常大于Die的尺寸

能夠起到良好的散熱效果

在部分的芯片當中,Die Pad有其它形狀(X形或窗口形PQFP)

Die Pad最好單獨建出,因為Die Pad與Leadframe或Trace間的

間距夠成明顯的熱阻

一定要考慮熱量在平面方向的熱傳遞,否則熱阻會增加15%

芯片的結構建模Die Attach

建模的建議

–忽略其在平面方面的熱傳遞,考慮其厚度方向的熱阻

–建為collapsed cuboid 或full cuboid

Die Attach夠成的熱阻比較明顯,尤其是金屬或陶瓷的芯片(如帶

有Lid或Cap的Flip-Chip PBGA,TBGA)

Die較小時,Die Attach也有相當的熱阻

芯片的結構建模Wire Bonds

陶瓷封裝芯片中可忽略

金屬較少的塑料封裝中導熱量較大

建議的建模方法

–建為各向導性的的立方體

在某些電源芯片中,需詳細建出(TO)

熱測試芯片Wire Bond較少,無法準確考慮其導熱效果

千萬不要低估Wire Bond的傳熱能力,在一些芯片如(2-layer PBGA’s (dieup),

PQFP),其傳熱量有可能占到總功耗的15%

芯片的結構建模Flip-Chip Bonding

倒裝焊技術起源于1960年IBM 公司

但從1980年以后才開始流行

Die通過焊球(Ball)直接與基片(Substrate)相連

–通常不是常規的陣列排布倒裝焊球

–常見的焊球材料: 37Pb/63Sn, 95Pb/5Sn

–常見的焊球直徑太概為is ~ 3 mils

芯片的結構建模倒裝互聯

倒裝焊的優勢和劣勢

–電氣性能好

–I/O數高,因為采用面陣列

–CTE(熱膨脹系數)不匹配是一個問題

–填充料(Underfill)的存在要求芯片不能返工

–價格昂貴(相對于Wire Bond PBGA)

建模方法

–熱阻較小,但必須建出(尤其是陶瓷芯片)

–不考慮倒裝層平面方向上的熱擴散

–作為collapsed cuboid 建模,采用體積平均的熱導系數

芯片的結構建模焊球(Solder Ball)

BGA 起源于1960年的IBM,1990年

后起為主流

球柵陣列(BGA)焊球可部分缺失

很少采用填充料Underfill

芯片的結構建模焊球(Solder Ball)

采用焊球的優缺點

–I/O數高

–電性能良好(自感較低)

–在回流焊接時可自動對齊,不良率低

–熱膨脹系數(CTE)不匹配

–難以發現加工缺陷

芯片的結構建模陶瓷基片

通常由氧化鋁制(k = 20 W/mK)

為了更好地散熱,材料也有可能是AlN 或BeO (k ~ 200 W/mK)

BeO 有毒,需特殊處理

陶瓷各層疊放在一起,放于高溫爐中燒制

其中金屬走線(traces)材料通常為鎢或鉬,對導熱影響很小,可忽略

建模時可將基片作為一整塊建出

熱量主要通過焊球導向PCB板

帶有散熱器的Capped C4/CBGA 芯片,通常一半以上的熱量流向散熱器

芯片的結構建模有機基片

將走線層定義為不同層

–不建議將整個基片都定義為一個立方體

在每個走線層,熱傳導系數大小取決于含銅體積率

芯片的結構建模過孔(Vias)

原用于增加PCB多層板的互聯

現也有于芯片內部

有點過孔也有于加強散熱(熱過孔)

芯片的結構建模過孔(Vias)

過孔分類

–信號過孔

–熱過孔

–單用于加強散熱

–通常為通孔

–一般聯接到熱焊球上

–位于Die Pad正下方最好

–在Wire-Bond PBGA中,如Die Pad下方有熱過孔,通常可忽略信號過孔的導熱

建模建議

–熱過孔對散熱影響很大

–信號過孔在某些情況下對散熱影響較大(如倒裝芯片)

–可將過孔詳細建出

–占用網格多

–建議

–將所有的過孔作為各項異性的立方塊

–不推薦

芯片的結構建模過孔(Vias)

芯片的結構建模Overmolding

材料為環氧樹脂

熱傳導系數較低(0.6 - 0.8 W/mK)

相當大的熱阻

為降低熱阻,通常在塑料芯片中放置內置的金屬散熱器

芯片的結構建模Leadframes

引線封裝(Lead Package)的標準部件

大多數具有Leadframe都是塑料芯片(PQFP, SOP, PLCC)

部分為陶瓷芯片(CQFP)

通常由銅制,部分為Alloy-42 (一種含鐵合金)

通常可使用立方塊統一建出

Leadframe 的聯接方式

–通常由Bond-Wire聯接到Die上

–在TAB封裝中使用TAB 聯接

–在最新的一些TSOP封裝中,Leadframe可使用絕緣膠直

接聯接至Die表面(Lead-on-Chip)

–如采用Wire-Bond封裝,則Die Pad與Leadframe為主要傳

熱瓶頸

芯片之外的結構建模PCB板

FLOPACK PCB smartpart 支持:

–任何數目的含銅層

–不限數目的過孔組

–Filled 或unfilled vias

–可將過孔組建為lumped 或discrete

–可參數化排列過孔

–PCB上表面為加強散熱的單獨銅層

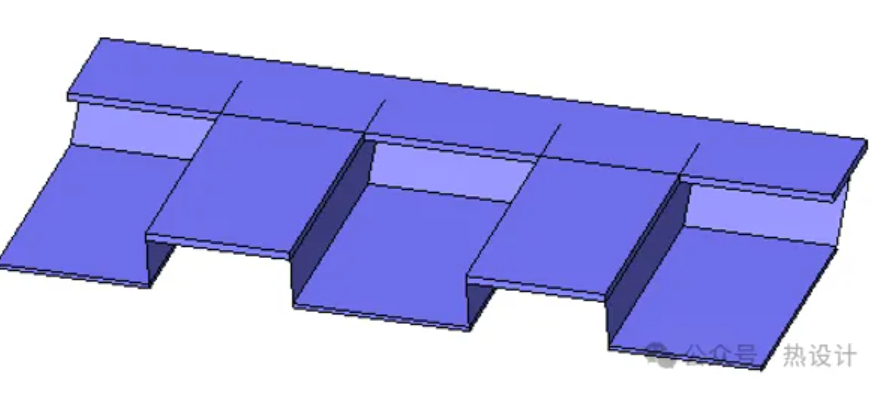

芯片之外的結構建模散熱器

進行散熱器選擇或設計時需考慮的因素

–充許的尺寸大小

–散熱器的熱阻Rsa

–接觸熱阻Interface Resistance

–擴散熱阻Spreading Resistance

–壓降Pressure Drop

–冷卻風流量Flow by pass

芯片之外的結構建模散熱器

幾種散熱器的熱阻和流阻

芯片之外的結構建模散熱器

例:快速進行片狀散熱器選型的經驗方法(Rules of Thumb)

–層流

–300K空氣溫度

對流換熱系數的估計公式

h = 1.26e-3 (V/H) 0.5 (W/in2 °C)

最小肋片間距的估計值

Smin = 1.3 (H/V) 0.5 (inches)

H = 空氣流動方向散熱器的長度(inches)

V = 空氣的接近流速(ft/min)

理想情況下散熱器的熱阻估算公式

R = 1/ ηhA

η =散熱器效率

R = 熱阻

A = 總表面積

h = 對流換熱系數

.

芯片之外的結構建模散熱器 P230

網格定義

肋片間網格數目定義:

1)2個網格:層流(溫度場誤差在10%以內)

2)3個網格:考慮了邊界層,較好地模擬了溫度性能

3)4-5個網格:較好地計算了散熱器的流阻.

高度方向:

1)為考慮散熱器底座的擴散熱阻,至少在散熱器的底座上加2個網格

2)肋高方向,3-4個網格一般就足夠了

肋片厚度方向的網格:

1)1個網格一般就可以了

芯片之外的結構建模散熱器

網格定義

散熱器壓力降:

1)肋片間的沿程壓力損失

2)肋片出入口忽擴忽縮壓力損失(主要)流體流動方向的壓力損失:

1)出入口處加密且不要形成網格間斷面

2)肋片出入口忽擴忽縮壓力損失(主要).

FLOPACK的功能

快速生成芯片模型-面陣列封裝及CSP封裝

Ball Grid Arrays and CSP’s:

–Plastic Ball Grid Array (PBGA) –

Wirebonded; with or without slug.

–PBGA - Flip-Chip, with or without lid

–PBGA - Cavity-Down, including

SuperBGATM

–PBGA - Stacked Die (TFBGA)

–Ceramic Ball Grid Array (CBGA) -

Wirebonded

–CBGA - Flip-Chip, with or without lid

–Tape Ball Grid Array (TBGA)

–ChipArrayTM also known as Fine Pitch BGA

(FPBGA) or FSBGA

–Board-on-Chip BOCTM

–MicroStarTM BGA

–MicroBGATM

–μZ-Ball StackTM

快速生成芯片模型-引線封裝(表面貼裝)

Leaded SMT

–Quad Flat No-Lead (QFN) or MLFTM

–Quad Flat Pack’s of various kinds including MQFP, LQFP, TQFP - with and without slugs.

–Small Outline packages such as SOIC, SOP,SSOP

–Thin Small Outline Package (TSOP) and

TSSOP; Conventional and Lead-on-Chip leadframes.

–Exposed Pad versions of popular QFP and SOIC/TSOP packages.

–Plastic Leaded Chip Carrier (PLCC).

快速生成芯片模型-穿孔安裝或功率芯片

Leaded Through-Hole

–PDIP

–CPGA - Cavity Up

–CPGA - Cavity Down

–CPGA - Flip Chip

Power Packages

–TO-220,

–TO-263 (D2PAK)

–TO-252 (DPAK)

–SOT-89

快速生成芯片模型-其它器件

Other parts

–PGA Socket

–Extruded Heatsink

–Pin Fin Heatsink

–Disk Fin Heat Sink

–PCB with user-defined layers and via clusters

–Bare die with multiple heat sources

.生成JEDEC標準測試環境

Standard JEDEC test environments

–Still Air

–Moving Air

–Ring Cold Plate

–Standard Test Boards (2S2P and 1S0P), etc.

FLOPACK 支持所有的JEDEC測試環境

生成2R或DELPHI等熱阻網格模型

DELPHI模型生成流程_FLOPACK

在FLOPACK選擇合適的封裝類型

選擇合適的JEDEC外觀尺寸

在明細單中修改具體的參數

下載后在FLOTHERM中修改參數

將修改過的模型上傳至FLOPACK

在FLOPACK生成修改模型的熱阻網絡模型

將熱阻網絡模型下載至FLOTHERM準備分析

Flotherm資料下載: FLOTHERM軟件高級培訓PPT.pdf

標簽: 點擊: 評論: